1. Jurnal [Kembali]

2. Alat dan Bahan [Kembali]

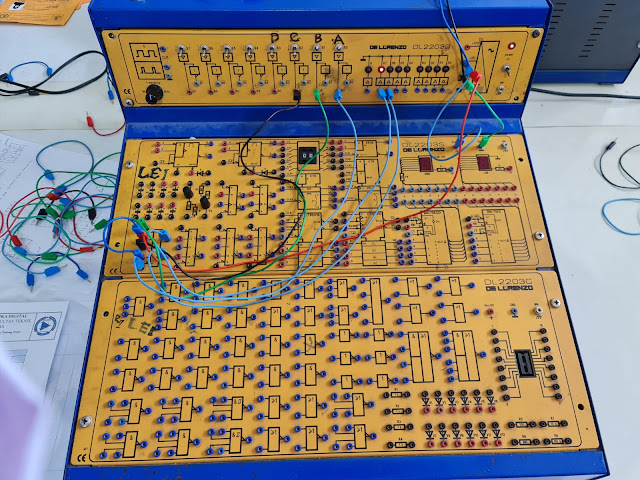

a. JK Flip Flop

b. DC Clock

c. Logic Probe

Logic probe atau logic tester adalah alat yang biasa digunakan untuk menganalisa dan mengecek status logika (High atau Low) yang keluar dari rangkaian digital.

d. Logic State

Gerbang Logika (Logic Gates) adalah sebuah entitas untuk melakukan pengolahan input-input yang berupa bilangan biner (hanya terdapat 2 kode bilangan biner yaitu, angka 1 dan 0) dengan menggunakan Teori Matematika Boolean sehingga dihasilkan sebuah sinyal output yang dapat digunakan untuk proses berikutnya.

3. Video Pratikum [Kembali]

4. Prinsip Kerja [Kembali]

Percobaan ini menggunakan J-K Flip Flop. Berdasarkan percobaan ini, kaki R (reset) dihubungkan ke B0 dengan logika 1, kaki S (set ) dihubungkan ke B1 dengan inputannya adalah 0 , kaki J dan K sama-sama dihubungkan ke VCC, kemudian untuk kaki CLK dihubungkan ke B2 dengan logika 1. Untuk outputnya yaitu untuk Q dihubungkan ke H7 dan untuk H6 dihubungkan ke 0. Jika disimulasikan maka untuk ouput yang dihasilkan adalah Q =1 dan Q'=0. Hal ini disebabkan karena CLK bersifat aktif low, dimana ia akan aktif saat berlogika 0. Karena pada kaki S (set), input yang diberikan adalah 0, maka itu akan mengaktifkan rangkaian yang bekerja pada kondisi aktif low, sehingga output yang dihasilkan berlogika 1. Pada percobaan ini, juga divariasikan beberapa keadaan seperti yang tertera pada jurnal.

5. Analisa [Kembali]

Analisa Percobaan 2:

1. Apa yang terjadi jika B1 diganti dengan CLK pada kondisi 2!

Jika B1 diganti dengan clock (S) yang terjadi untuk output yang dihasilkan adalah Q=1 danQ'=0. Ini berlaku saaat logika 1. Sedangkan, jika clocknya berlogika 0 maka outputnya akan berubah Q=0 dan Q'=1. Ini bukan toggle karena hanya terjadi sebentar saja.

2. Bandingkan hasil percobaan dengan teori.

- Saat T Flip Flop dalam mode asinkronus reset, dengan nilai adalah 0 maka outputnya Q=0 dan Q'=1 (sesuai dengan teori)

- Saat T Flip Flop dalam mode asinkronus set, dengan nilai inputnya 0 maka outputnya Q=1 dan Q'=1 (sesuai dengan teori)

- Saat T Flip-Flop dalam kondisi terlarang, dengan nilai inputnya maka outputnya adalah Q=1 dan Q'= 1 (sesuai dengan teori)

- Saat T Flip-Flop dalam kondisi Toggle yaitu output Q berubah berdasarkan output T nya. Dalam percobaan terlihat bahwa ketika input T berlogika 1 maka outputnya membalikkan nilai output dan T yaitu 0. Sedangkan jika input T berlogika 0 maka outputnya tidak dibalikkan atau tetap (sesuai dengan teori)

5. Link Download [Kembali]

.png)

.png)

.png)

Tidak ada komentar:

Posting Komentar